As FPGAs become more common in mainstream general-purpose computing platforms,

capturing and distributing high-performance implementations of applications on

FPGAs will become increasingly important. Even in the presence of C-based synthesis

tools for FPGAs, designers continue to implement applications as circuits, due in

large part to allow for capture of clever spatial, circuit-level implementation

features leading to superior performance and efficiency. We demonstrate the

feasibility of a spatial form of FPGA application capture that offers portability

advantages for FPGA applications unseen with current FPGA binary formats. We

demonstrate the portability of such a distribution by developing a fast on-chip

emulation framework that performs transparent optimizations, allowing spatially-captured

FPGA applications to immediately run on FPGA platforms without costly and hard-to-use

synthesis/mapping tool flows, and sometimes faster than PC-based execution. We

develop several dynamic and transparent optimization techniques, including just-in-time

compilation, bytecode acceleration, and just-in-time synthesis that take advantage of

a platform's available resources, resulting in orders of magnitude performance

improvement over normal emulation techniques and PC-based execution.

SystemC-on-a-Chip is a virtual platform framework that enables a student/designer

to write SystemC applications at the logic, register transfer, behavioral or

structural level, and immediately test that design on any real platform with real

input/output that supports the virtual platform.

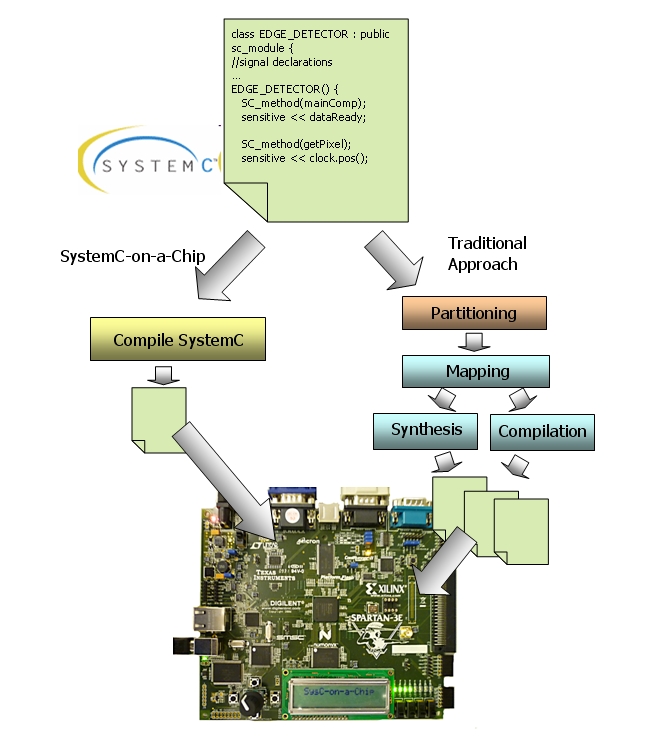

In contrast to more traditional system design approaches, the SystemC-on-a-Chip

framework does not rely on costly and difficult-to-use mapping/synthesis tool suites.

Instead, SystemC applications are compiled and interpreted, allowing a designer to

write, compile, and download a design to a real platform in minutes, and with access

to all the real peripherals just as if the designer had actually mapped and synthesized

the design to the platform. The SystemC-on-a-Chip framework thus allows for quick

prototyping and testing on the real platform, complementing the simulation process

on a standard PC and the final implementation on the platform.

The SystemC-on-a-Chip framework can be useful in beginning digital design,

embedded systems, and parallel computing courses, allowing students to focus

on fundamental and good design/programming practices, and not on the often

complex and difficult-to-use design flows for traditional platform programming

that hinder productivity and cause frustration. Students with a background in C++

development will find SystemC more approachable than traditional hardware description

languages(HDL) like VHDL or Verilog. Similarly, the SystemC-on-a-Chip framewrok

compiles SystemC applications in seconds using a very familiar compilation process

built on top of GCC. The SystemC-on-a-Chip framework can be used in conjunction

with existing software simulation practices to give the user the satisfaction of

seeing a design work on a real platform, and in a much more timely and simpler manner.

The SystemC-on-a-Chip framework can be useful in beginning digital design,

embedded systems, and parallel computing courses, allowing students to focus

on fundamental and good design/programming practices, and not on the often

complex and difficult-to-use design flows for traditional platform programming

that hinder productivity and cause frustration. Students with a background in C++

development will find SystemC more approachable than traditional hardware description

languages(HDL) like VHDL or Verilog. Similarly, the SystemC-on-a-Chip framewrok

compiles SystemC applications in seconds using a very familiar compilation process

built on top of GCC. The SystemC-on-a-Chip framework can be used in conjunction

with existing software simulation practices to give the user the satisfaction of

seeing a design work on a real platform, and in a much more timely and simpler manner.