### UNIVERSITY OF CALIFORNIA RIVERSIDE

Emulation of SystemC Applications for Portable FPGA Binaries

A Dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

by

Scott Spencer Sirowy

June 2010

Dissertation Committee: Dr. Frank Vahid, Chairperson Dr. Tony Givargis Dr. Sheldon X.-D. Tan

Copyright by Scott Spencer Sirowy 2010 The Dissertation of Scott Spencer Sirowy is approved:

Committee Chairperson

University of California, Riverside

#### ABSTRACT OF THE DISSERTATION

Emulation of SystemC Applications for Portable FPGA Binaries

by

Scott Spencer Sirowy

#### Doctor of Philosophy, Graduate Program in Computer Science University of California, Riverside, June 2010 Dr. Frank Vahid, Chairperson

As FPGAs become more common in mainstream general-purpose computing platforms, capturing and distributing high-performance implementations of applications on FPGAs will become increasingly important. Even in the presence of C-based synthesis tools for FPGAs, designers continue to implement applications as circuits, due in large part to allow for capture of clever spatial, circuit-level implementation features leading to superior performance and efficiency. We demonstrate the feasibility of a spatial form of FPGA application capture that offers portability advantages for FPGA applications unseen with current FPGA binary formats. We demonstrate the portability of such a distribution by developing a fast on-chip emulation framework that performs transparent optimizations, allowing spatially-captured FPGA applications to *immediately* run on FPGA platforms without costly and hard-to-use synthesis/mapping tool flows, and sometimes faster than PC-based execution. We develop several dynamic and transparent optimization techniques, including *just-in-time compilation, bytecode acceleration*, and *just-in-time synthesis* that take advantage of a platform's available resources, resulting in

orders of magnitude performance improvement over normal emulation techniques and PC-based execution.

# Table of Contents

| Chapter 1 |                                                                   | . 1 |

|-----------|-------------------------------------------------------------------|-----|

| Chapter 2 | /                                                                 | 11  |

| 2.1       | Overview                                                          | 11  |

| 2.2       | C is for Circuits                                                 | 11  |

| 2.2.1     | Overview                                                          | 11  |

| 2.2.2     | A Motivating Example – Sorting                                    | 15  |

| 2.2.3     |                                                                   |     |

| 2.2.4     | Example – Gaussian Noise Generator                                | 21  |

| 2.2.5     | Example – Molecular Dynamics Simulator                            | 27  |

| 2.2.6     | Example - Cellular Learning Automata-Based Evolutionary Computing | 29  |

| 2.2.7     |                                                                   |     |

| 2.3       | Other Related Work                                                | 37  |

| 2.3.1     | C-based Synthesis Tools                                           | 37  |

| 2.3.2     | Parallel Languages                                                | 38  |

| 2.3.3     | B Portability                                                     | 38  |

| 2.4       | Requirements of a Language for Spatial Capture                    | 39  |

| 2.4.1     | POSIX                                                             | 41  |

| 2.4.2     | 2 Other Thread-Based Approaches                                   | 43  |

| 2.4.3     | SystemC                                                           | 44  |

| Chapter 3 | · · · · · · · · · · · · · · · · · · ·                             | 47  |

| 3.1       | Overview                                                          | 47  |

| 3.2       | Related Work                                                      | 50  |

| 3.3       | SystemC-on-a-Chip Components                                      | 51  |

| 3.3.1     | SystemC Bytecode Compiler                                         | 51  |

| 3.3.2     | 2 SystemC Bytecode Format                                         | 53  |

| 3.3.3     | USB Download Interface                                            | 57  |

| 3.3.4     | SystemC Emulation Engine                                          | 58  |

| 3.4       | Experiments                                                       | 61  |

| Chapter 4 | -                                                                 | 65  |

| 4.1       | Overview                                                          | 65  |

| 4.2       | Related Work                                                      | 68  |

| 4.3       | Online SystemC Emulation Architecture                             | 70  |

| 4.3.1     | Base Architecture with Acceleration Engines                       | 70  |

| 4.3.2     |                                                                   |     |

| 4.4       | Online Acceleration Assignment                                    | 73  |

| 4.4.1     | -                                                                 |     |

| 4.4.2     | 2 Communication Overhead                                          | 76  |

| 4.5       | Online Heuristics                                                 |     |

| 4.5.1     | Upper and Lower Bounds                                            | 76  |

| 4.5.2     | 2 Accelerator Static Assignment                       | 77  |

|-----------|-------------------------------------------------------|-----|

| 4.5.3     | 3 Greedy Heuristic                                    | 77  |

| 4.5.4     | 4 Aggregate Gain                                      |     |

| 4.6       | Experiments                                           | 79  |

| 4.6.1     | Framework                                             | 79  |

| 4.6.2     | 2 Evaluation                                          | 81  |

| Chapter 5 | 5                                                     | 84  |

| 5.1       | Overview                                              | 84  |

| 5.2       | Related Work                                          | 86  |

| 5.3       | Experimental Setup                                    | 87  |

| 5.4       | Just-in-Time Compilation of SystemC                   | 89  |

| 5.4.1     |                                                       |     |

| 5.4.2     | 2 JIT Compilation with Dedicated JIT Memory Resources | 91  |

| 5.4.3     | 3 Emulation Memory Controller                         | 94  |

| Chapter 6 | 5                                                     | 98  |

| 6.1       | Overview                                              | 98  |

| 6.2       | Related Work                                          | 99  |

| 6.3       | Just-in-Time Synthesis                                | 101 |

| 6.3.1     | 1 Server-Side Synthesis Framework                     | 101 |

| 6.3.2     | 2 Decompilation and Synthesis                         | 104 |

| 6.3.3     | 3 SystemC-on-a-Chip Architectural Support             | 105 |

| 6.4       | Experiments                                           | 108 |

| Chapter 7 | 7                                                     | 111 |

| 7.1       | Overview                                              | 111 |

| 7.2       | SystemC for Synchronized Physiological Models         | 115 |

| 7.3       | Related Work                                          | 118 |

| 7.4       | Time-Controllable Digital Mockup Execution            | 119 |

| 7.5       | Experiments                                           | 121 |

| Chapter 8 | 3                                                     | 126 |

| 8.1       | Overview                                              | 126 |

| 8.2       | Related Work                                          | 127 |

| 8.3       | SystemC-on-a-Chip Software                            | 129 |

| 8.3.1     | Using the SystemC Bytecode Compiler                   |     |

| 8.3.2     |                                                       |     |

| 8.4       | Spatial and Time-Oriented Programming                 | 132 |

| 8.4.1     | l Course Plan                                         | 132 |

| 8.4.2     | L                                                     |     |

| Chapter 9 |                                                       |     |

| 9.1       | Summary                                               |     |

| 9.2       | Remaining Challenges                                  | 137 |

## List of Figures

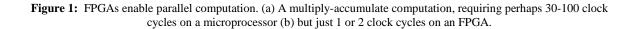

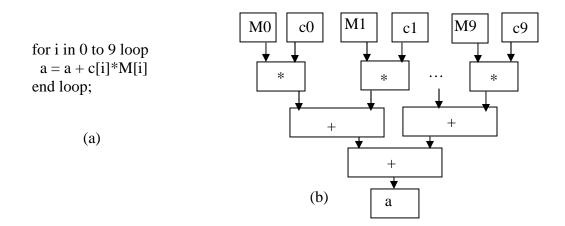

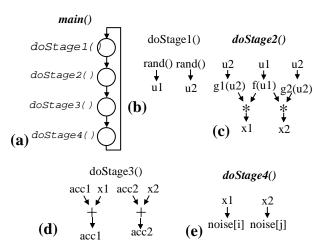

Figure 1: FPGAs enable parallel computation. (a) A multiply-accumulate computation, requiring perhaps 30-100 clock cycles on a microprocessor (b) but just 1 or 2 clock Figure 2: Although temporally-oriented algorithms in C can be synthesized to a variety of circuits trading off size and performance, many clever circuits representing spatiallyoriented algorithms are not reasonably derivable from temporally-oriented algorithms. 12 Figure 3: C is for circuits: Some circuits might still be captured in a form of C code that is synthesizable back to the original circuit; such C code would provide tremendous Figure 4: Study methodology. We modeled each circuit in C (when possible). We then performed the following transformations and optimizations in the order shown, representing a "standard" synthesis tool, and observed whether the original circuit was Figure 7: Control/data flow graph for C-level Gaussian noise generator functions (a) main, (b) doStage1, (c) doStage2, (d) doStage3, and (e) doStage4......24

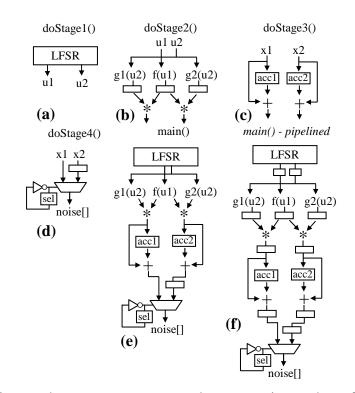

| Figure 8: Datapaths after scheduling, resource allocation, and binding for (a) doStage1,   |  |  |  |

|--------------------------------------------------------------------------------------------|--|--|--|

| (b) doStage2, (c) doStage3, (d) doStage3, (e) main before pipelining, and (f) main after   |  |  |  |

| pipelining. Note the similarity with Figure 5                                              |  |  |  |

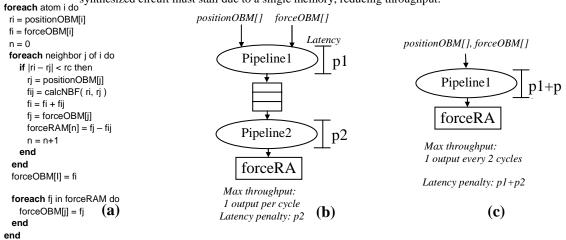

| Figure 9: Molecular dynamics accelerator. (a) Code for calculating nonbonded forces. (b)   |  |  |  |

| Custom circuit utilizing a divided pipeline to reduce latency penalty. (c) The synthesized |  |  |  |

| pipeline differs from the custom circuit by utilizing a single pipeline. The synthesized   |  |  |  |

| circuit must stall due to a single memory, reducing throughput                             |  |  |  |

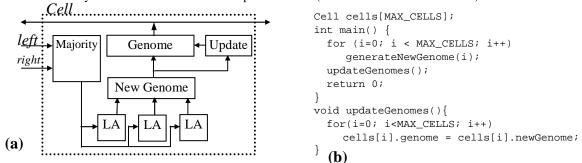

| Figure 10: The proposed custom CLA-EC circuit consisting of a ring of (a) custom CLA-      |  |  |  |

| EC cells and (b) C pseudocode that synthesizes to an almost identical parallel circuit     |  |  |  |

| (code for cell internals is omitted)                                                       |  |  |  |

| Figure 11: 82% of the studied circuits published in FCCM were re-derivable from C,         |  |  |  |

| meaning they could be captured in some form of C such that a synthesis tool could be       |  |  |  |

| expected to synthesize the same or similar custom design                                   |  |  |  |

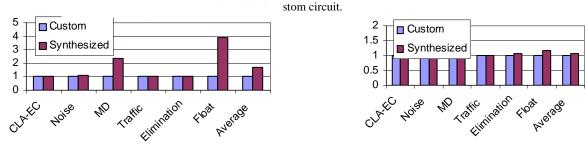

| Figure 12: Comparison of original custom circuits versus circuits synthesized from         |  |  |  |

| derived sequential code representations: (a) Normalized xecution time and (b)              |  |  |  |

| Normalized area (slices) Both metrics are normalized to values for the original custom     |  |  |  |

| circuit                                                                                    |  |  |  |

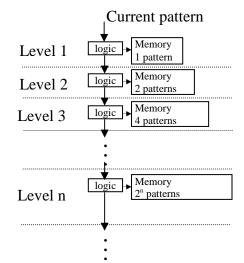

| Figure 13: Pipelined Binary Tree [94]. Each level operates concurrently, taking the        |  |  |  |

| pattern and address information from the previous level, and passing information to the    |  |  |  |

| next level. Such a design cannot readily be captured in a sequential language, and         |  |  |  |

| requires explicit parallel constructs to capture for portable distribution                 |  |  |  |

| Figure 14: Snippet of POSIX-based implementation of one level of the pipelined binary     |

|-------------------------------------------------------------------------------------------|

| tree and how levels are connected and how they communicate                                |

| Figure 15: Snippet of SystemC implementation of a level of the pipelined binary tree and  |

| how multiple levels are connected                                                         |

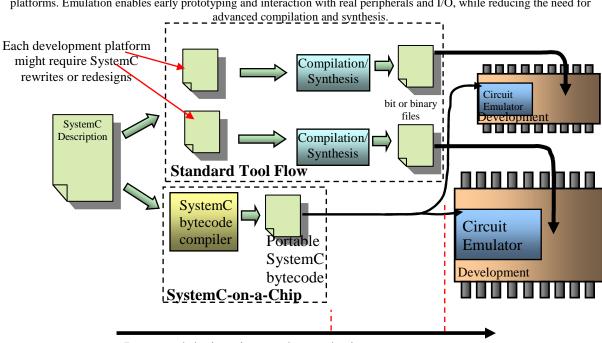

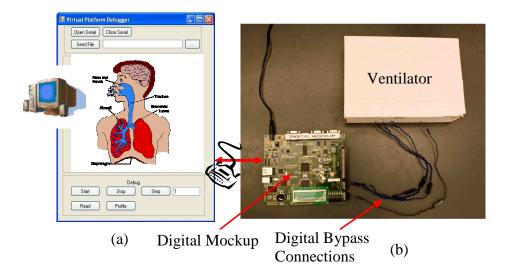

| Figure 16: SystemC-on-a-Chip allows a designer to emulate SystemC descriptions on         |

| various supported development platforms. Emulation enables early prototyping and          |

| interaction with real peripherals and I/O, while reducing the need for advanced           |

| compilation and synthesis                                                                 |

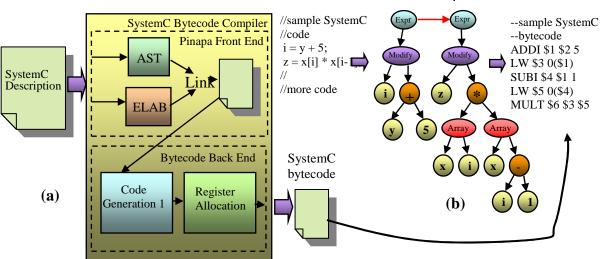

| Figure 17: SystemC bytecode compiler: (a) The SystemC bytecode compiler builds on         |

| PINAPA, a SystemC front-end tool, and uses a custom SystemC bytecode backend; (b)         |

| Sample code generation during the first phase of the SystemC bytecode back end 52         |

| Figure 18: SystemC bytecode format. Each process is described by a number of MIPS-        |

| like instructions, with additional instructions added for SystemC specifics, like reading |

| signals, extracting bit ranges, etc                                                       |

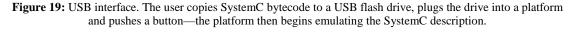

| Figure 19: USB interface. The user copies SystemC bytecode to a USB flash drive, plugs    |

| the drive into a platform and pushes a button—the platform then begins emulating the      |

| SystemC description                                                                       |

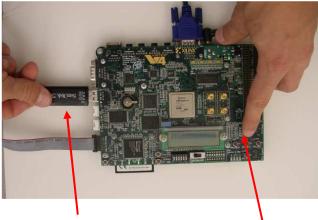

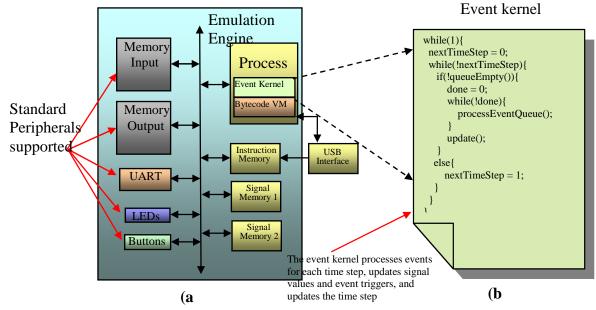

| Figure 20: Basic emulation engine. The emulation engine consists of a hybrid event-       |

| driven kernel to allow a variety of different circuit implementations. Circuits can also  |

| take advantage of a range of standard peripherals, including lights, buttons, a UART, and |

| input and output memories                                                                 |

| Figure 21: SystemC-on-a-Chip circuit interface. The emulation engine supports access to     |

|---------------------------------------------------------------------------------------------|

| multiple peripherals, including buttons, LEDs, and memory                                   |

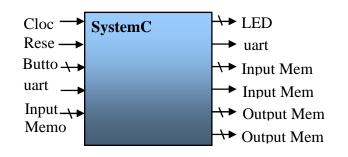

| Figure 22: SystemC-on-a-Chip prototypes. Each system differed in size, processor,           |

| memory, and number of emulation accelerators, but each could run the same SystemC           |

| bytecode for a given SystemC description                                                    |

| Figure 23: SystemC experiments. (a) SystemC code for Image Edge Detection. The code         |

| took only minutes to create and compile before being put on a Virtex4. (b) Edge             |

| Detection running on a Virtex4. We connected the memory output to a frame buffer to         |

| see the results on a VGA screen                                                             |

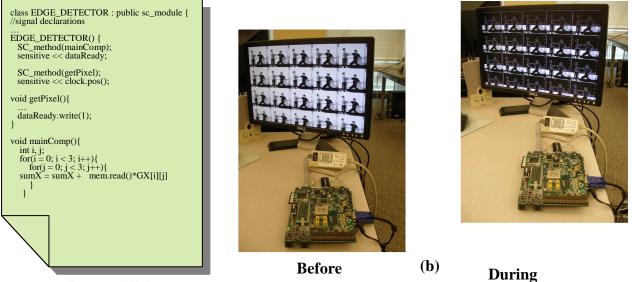

| Figure 24: Emulation accelerators. The emulation accelerator consists of a multicycle       |

| MIPs-like datapath than can execute one instruction in about 3-4 cycles, almost 100X        |

| faster than executing the same instructions in the base emulator                            |

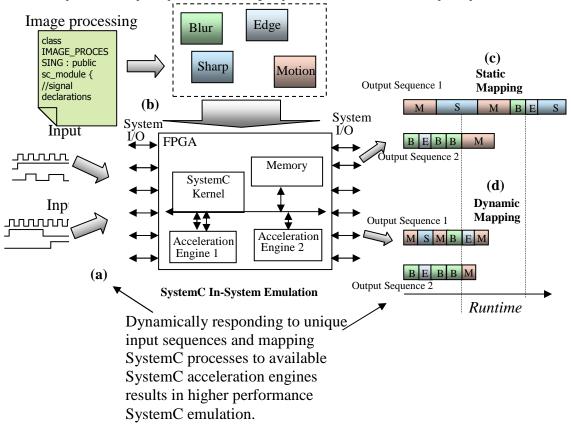

| Figure 25: SystemC in-system emulation: (a) In-system emulation of a description            |

| allows testing with real I/O, thus creating dynamic test bench input vectors that cannot be |

| analyzed statically. (b) Sample image processing system that invokes several different      |

| filters depending on the input. (c) Statically mapping each process to either software or   |

| an acceleration engine results in widely varied runtimes for different input sequences. (d) |

| Dynamically mapping SystemC processes in response to the input sequence results in          |

| higher performance emulation for all input sequences                                        |

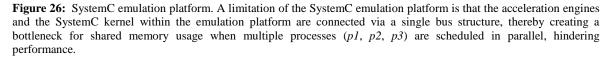

| Figure 26: SystemC emulation platform. A limitation of the SystemC emulation platform       |

| is that the acceleration engines and the SystemC kernel within the emulation platform are   |

| connected via a single bus structure, thereby creating a bottleneck for shared memory       |

| usage when multiple processes $(p1, p2, p3)$ are scheduled in parallel, hindering         |  |  |  |

|-------------------------------------------------------------------------------------------|--|--|--|

| performance70                                                                             |  |  |  |

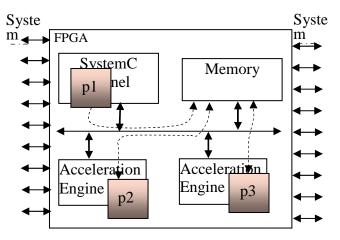

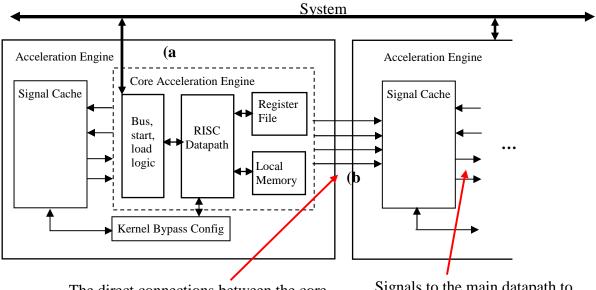

| Figure 27: SystemC acceleration engines: (a) Internal structure. (b) Direct connection of |  |  |  |

| two SystemC acceleration engines using a kernel bypass connection. In some situations,    |  |  |  |

| bypassing the bus and SystemC kernel can lead to significant performance benefits for a   |  |  |  |

| given SystemC description71                                                               |  |  |  |

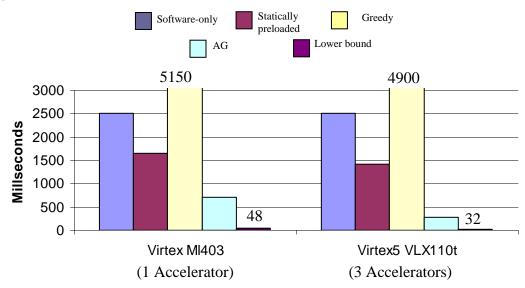

| Figure 28: Emulation runtime results of image filtering, lung, and radiosity examples     |  |  |  |

| emulated on two different emulation platforms. AG performs up to 9x faster than           |  |  |  |

| software-only emulation, and 5x faster than a <i>statically preloaded</i> approach        |  |  |  |

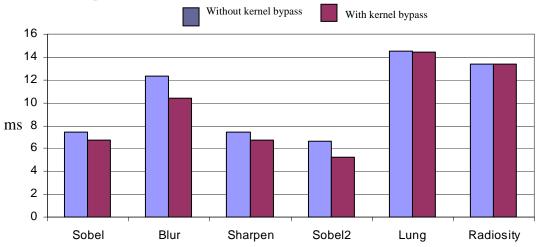

| Figure 29: Emulation runtimes without and with kernel bypass using the AG heuristic on    |  |  |  |

| the image processing examples. Kernel-bypass-enabled emulations performed on average      |  |  |  |

| 11% better than without kernel bypass, and up to 20% in some examples                     |  |  |  |

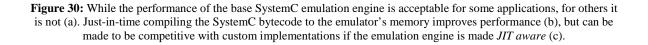

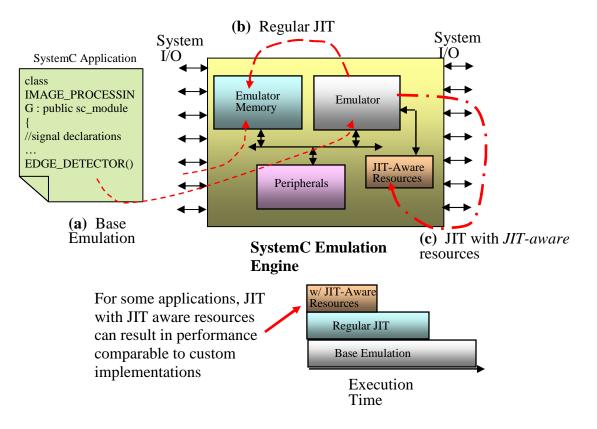

| Figure 30: While the performance of the base SystemC emulation engine is acceptable       |  |  |  |

| for some applications, for others it is not (a). Just-in-time compiling the SystemC       |  |  |  |

| bytecode to the emulator's memory improves performance (b), but can be made to be         |  |  |  |

| competitive with custom implementations if the emulation engine is made JIT aware (c).    |  |  |  |

|                                                                                           |  |  |  |

| Figure 31: The JIT/architecture codesign process                                          |  |  |  |

| Figure 32: Experimental Prototypes. (a) The Virtex5 vlx110t implementation connected      |  |  |  |

| to a large screen buffer for testing image processing applications. (b) A summary of each |  |  |  |

| experimental system. Each version was built with and without dedicated hardware to        |  |  |  |

| improve the impact of just-in-time compilation of the SystemC bytecode                    |  |  |  |

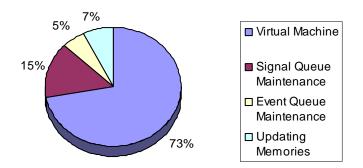

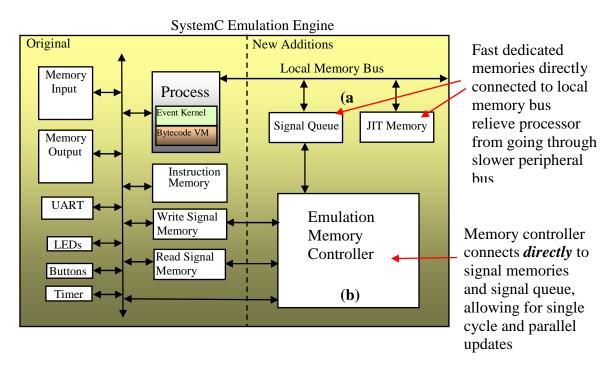

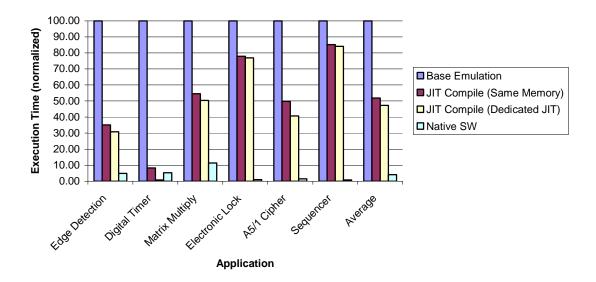

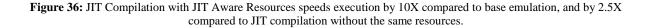

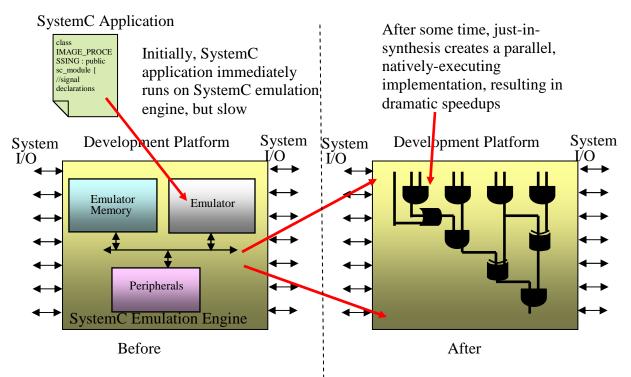

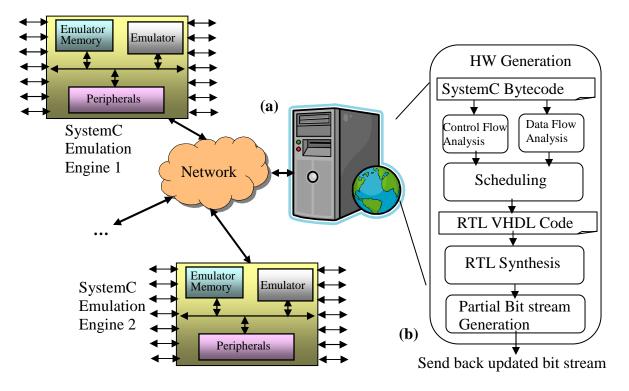

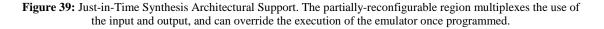

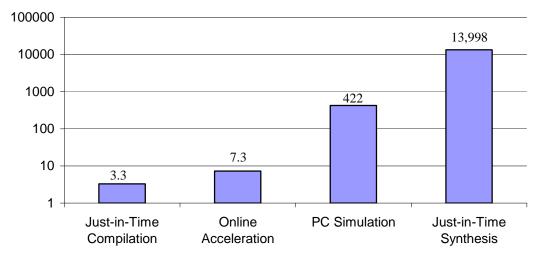

Figure 34: Modifications to the SystemC emulation engine that increase the utility of just-in-time compilation. The new SystemC emulation engine supports a local memory bus with a dedicated JIT memory and a static signal queue for fast access to commonly executed software operations (a). The new SystemC emulation engine also has a dedicated *emulation memory controller*, which offloads costly memory updates from Figure 35: JIT compilation with dedicated JIT resources performed 4X faster than the base SystemC emulation platform, yet still fell short of native software implementations Figure 36: JIT Compilation with JIT Aware Resources speeds execution by 10X compared to base emulation, and by 2.5X compared to JIT compilation without the same Figure 37: Just-in-Time Synthesis of SystemC applications leads to natively executing applications that can run orders of magnitude faster than baseline simulation and several Figure 38: Just-in-Time Synthesis SystemC-on-a-Chip framework. (a) The server responds to requests from SystemC-on-a-Chip platforms that require native execution speeds. (b) The server *decompiles* the SystemC bytecode, recovers the high-level information, and synthesizes a circuit tuned to that platform's available resources. ..... 103

| Figure 39: Just-in-Time Synthesis Architectural Support. The partially-reconfigurable      |

|--------------------------------------------------------------------------------------------|

| region multiplexes the use of the input and output, and can override the execution of the  |

| emulator once programmed                                                                   |

| Figure 40: Speedups compared to base SystemC emulation for some common image               |

| processing filters. Factoring out the time required to synthesize the SystemC application, |

| just-in-time synthesis is almost 14,000X faster than base emulation, and 30X faster than   |

| PC simulation                                                                              |

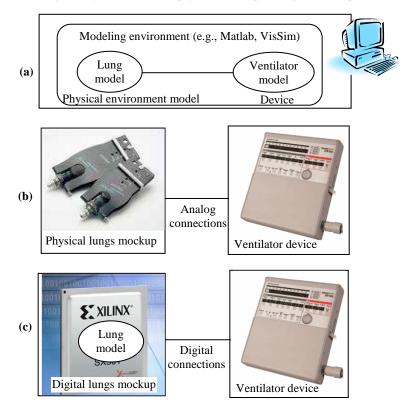

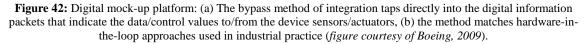

| Figure 41: Approaches to integrating an embedded device with the physical environment      |

| during design: (a) system model, (b) physical mockup, (c) digital mockup 112               |

| Figure 42: Digital mock-up platform: (a) The bypass method of integration taps directly    |

| into the digital information packets that indicate the data/control values to/from the     |

| device sensors/actuators, (b) the method matches hardware-in-the-loop approaches used      |

| in industrial practice (figure courtesy of Boeing, 2009) 114                               |

| Figure 43: Capturing physiological models in SystemC. (a) Portion of a mathematical        |

| model of the human lung. (b) Description of the model in SystemC. (c) Description using    |

| POSIX threads. The POSIX threads approach requires implementing explicit lock-             |

| stepping mechanisms that detract from the model's readability 116                          |

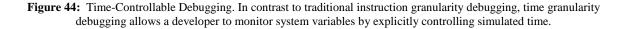

| Figure 44: Time-Controllable Debugging. In contrast to traditional instruction             |

| granularity debugging, time granularity debugging allows a developer to monitor system     |

| variables by explicitly controlling simulated time                                         |

| Figure 45: SystemC Implementation of a two-compartment respiratory system digital          |

| mockup                                                                                     |

| Figure 46: SystemC Digital Mockup Implementation Summary. Both respiration models      |

|----------------------------------------------------------------------------------------|

| were obtained from the NSR Physiome Project and manually converted to concurrently     |

| executing SystemC implementations                                                      |

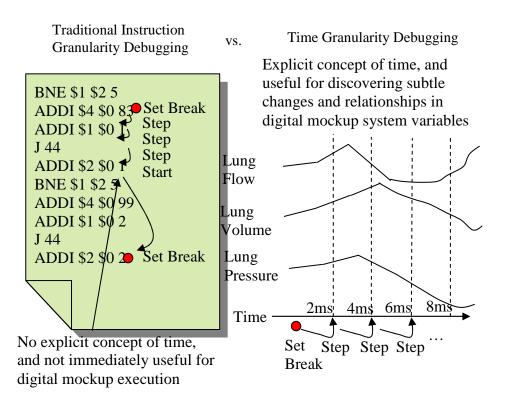

| Figure 47: Medical device(ventilator) and digital mockup(lung) prototype setup. (a)The |

| digital mockup can be time-controlled using a simple PC-based debug interface. (b)The  |

| digital mockup and ventilator communicating digitally125                               |

| Figure 48: SystemC-on-a-Chip in the classroom                                          |

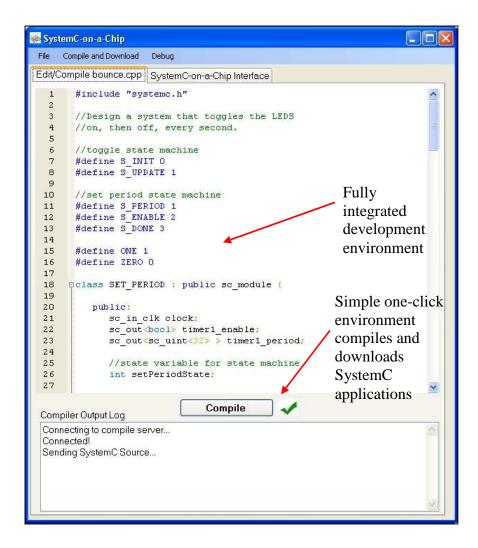

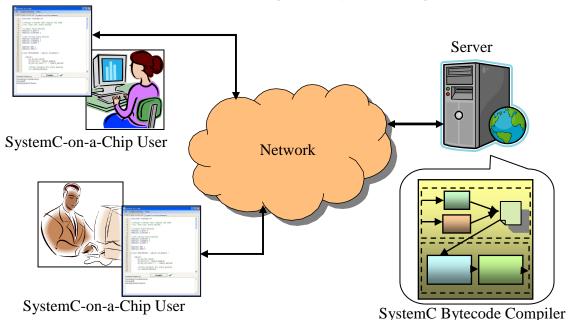

| Figure 49: Windows-based interface for programming SystemC-on-a-Chip 129               |

| Figure 50: Remote Compilation for SystemC-on-a-Chip                                    |

| Figure 51: Time Oriented and Spatial Programming with SystemC. We have developed a     |

| complete set of labs and materials to complement a course in spatial and time-oriented |

| programming                                                                            |

### Chapter 1

### Introduction

FPGAs (field-programmable gate arrays) support a new form of software whose order of magnitude speedups can enable a class of new high-performance embedded applications not otherwise feasible. However, unlike microprocessor software, two problems severely limit FPGA adoption, and thus prevent the appearance of a range of useful embedded applications. The first problem is that of a highly specialized design process for FPGAs that differs greatly from microprocessor software design, a problem that has been intensively studied by researchers and for which commercial solutions are beginning to appear. The second problem is that FPGA binaries are presently intricately coupled with specific FPGA devices, and cannot be ported across devices or migrated to newer device versions the way that microprocessor binaries can.

FPGAs implement circuits, characterized through their spatial connectivity: component A is connected to B, which is connected to C, etc. Each component computes

in *parallel* with all the other components, of which there may be thousands. In contrast, microprocessors implement sequential programs, characterized by their *serial* ordering of computations as a sequence of instructions. It is the parallelism, from the task level down to the bit level, that contributes to FPGAs executing certain computations orders of magnitude faster than microprocessors.

Figure 1 illustrates a computation involving 10 multiplications and additions, which might require 30 to 100 clock cycles to execute on a microprocessor, but could execute in just 1 or 2 clock cycles on an FPGA if enough resources existed. Many embedded system applications are especially amenable to computation speedup from FPGAs. For example, an image processing application may search a camera-provided image for specific objects, such as a tank, a person, or even a specific person's face. Algorithms for such applications may identically search local image portions and then hierarchically compose results – those local search tasks are typically highly-parallelizable, and hence image processing algorithms may execute hundreds of times

faster on an FPGA than on a microprocessor. Likewise, highly parallelizable subtasks exist in other common embedded applications that involve processing streams of video, audio, speech, and other data. Sample domains include television set-top boxes, security cameras, medical imaging and diagnosis equipment, contraband detection systems at locations like airports or borders, fingerprint recognition, speech understanding, and a wide range of military applications. Extensive previous work has shown the speedup advantages of FPGA, typically 10x to 100x, for a wide range of embedded applications [REFS]. Such order-of-magnitude speedups may not just be a change in speed, but rather a "change in kind," as von Neumann originally described the impact of computers over existing desktop calculators, enabling applications not before possible (i.e., the applications enabled by a computer's speed far exceed categorization as that of merely a fast desktop calculator).

One recognized problem preventing FPGA adoption is the different, and more complex, design flow for FPGAs compared to that for microprocessors. The typical design flow requires FPGA users to describe the desired circuit in a hardware description language (HDL), such as VHDL or Verilog, and to use special FPGA-vendor-provided compilers (known as synthesis tools) that convert HDL descriptions to device-specific FPGA binaries. In contrast, microprocessor users utilize "standard" programming languages like C, C++, or Java, and utilize robust high-quality compilers and integrated development environments (IDEs) typically developed by third-party vendors who often specialize in such tools. The massive microprocessor hardware, applications, and tools industries, whose importance need not be stated, have been strongly catalyzed by the

separation of architecture from function enabled by the concept of microprocessor instruction sets, enabling a *standard microprocessor binary*. A standard microprocessor binary is a binary written using instructions of an instruction set, such as an x86 or ARM processor instruction set, that can execute on a variety of existing and evolving versions of a microprocessor, leading to benefits and innovations in the creation of architectures, tools, and applications.

Today, software for FPGAs does *not* benefit from the standard binary concept. Instead, software is compiled by FPGA-vendor-provided tools (typically for free as a means of selling hardware devices), into a proprietary binary that is intricately bound to a specific device. A vendor may offer dozens or hundreds of different devices – Xilinx for example presently supports approximately 100 devices. A binary created for one device cannot run on any other device. The situation hampers development of architecture, software, and tools, and thus the widespread use of FPGAs for embedded computing platforms.

It's natural to ask why industry has not already developed a standard binary concept, if the concept would be so useful. In fact, we do believe that such a concept would eventually begin to evolve over the coming 10-20 year period, with small bitstream portability techniques accumulating into something akin to a standard binary. The lack of portable binaries is becoming recognized as a problem hampering FPGA adoption. For example, an FPGA panel at Supercomputing 2005 noted: "Most applications outlive the hardware. If one is going to invest in an [FPGA] accelerator, what are the options when the accelerator is obsolete? It's a very real issue" [110]. Extensive discussions regularly appear in the newsgroup comp.arch.fpga, and designers have organized to try to make FPGA internal architectures more open (e.g., [109]).

A standard binary concept for FPGAs will certainly incur performance and size overhead compared to the current desktop FPGA CAD approach. Yet, a standard binary concept for FPGAs may catalyze the FPGA hardware, applications, and tools industries, similar to how it catalyzes the microprocessor domain, thus compensating for the incurred overhead. Furthermore, a standard binary for FPGAs that seamlessly integrates with that for microprocessors, may catalyze incorporation of FPGAs into the massive established microprocessor industry, whose hardware and software revenues and number of application developers tower over those for FPGAs by two orders of magnitude. The net result would be the widespread use of FPGAs, especially in embedded systems, whose applications are particularly amenable to FPGA speedup, and hence the appearance of high-performance embedded applications that would otherwise not be developed due to the difficulty of utilizing FPGAs.

We envision opportunities for a portable FPGA distribution format that rides on the success of the "write once, run everywhere" programming paradigm of interpreted languages like Java and C#, wherein a designer captures a design in a high level language, and *any* computing platform that supports a virtual machine for that language can execute that application. At the expense of initial performance, virtual machine technology (like Java's JVM) enables great portability, and is promising as the foundation for a portable FPGA binary. We introduce tools and techniques for an emulation framework that allows for portable FPGA binary execution which we call *SystemC-on-a-Chip*.

This dissertation can logically be broken into three distinct sections. The first section only includes Chapter 2, and investigates spatial programming and the proper programming constructs and requirements to facilitate a standard FPGA distribution format, and the reasons for choosing SystemC as a possible distribution language. The second section comprises Chapters 3, 4, 5, and 6, and describes tools, frameworks, and experiments to enable the emulation of applications developed in SystemC. Finally, the last section, comprising Chapters 7 and 8, investigate additional uses of the SystemC-on-a-Chip framework.

In Chapter 2, we present an investigation into the proper constructs and languages required to facilitate a portable distribution format for FPGA-based applications. We present a study entitled "C is for Circuits" that closely studied 70 custom-created, clever circuits and attempted to capture those circuits in a sequential language such that a standard C-to-gates synthesis tool could recreate the original custom circuit. Our study complements the question asked by many researchers on whether sequential code (like C) can be analyzed and translated into a high performance circuit. Our study showed that while many custom-created circuits could actually be captured using a sequential language, others could not readily be translated and relied on explicit parallel concepts. Of those that could be translated to a sequential language, many required a radical algorithm change to facilitate synthesis. We thus determined that a portable distribution format would require both *temporal* and *spatial* constructs. We then

investigate the requirements of a language suitable for spatial capture of FPGA applications. We investigate the feasibility of using popular parallel programming frameworks like POSIX, MPI, and RTOS's, but conclude that the SystemC language best captures the temporal and spatial concepts required of a standard FPGA distribution format.

In Chapter 3, we introduce SystemC-on-a-Chip, a framework that allows a designer to capture applications in SystemC and have them *immediately* run on any platform that supports the SystemC emulation engine. We introduce the newly developed SystemC bytecode (analogous to Java bytecode), a lean intermediate representation of the SystemC application that preserves both the temporal and spatial features of the application. The SystemC bytecode facilitates a portable representation of the SystemC application that can run any platform assuming SystemC bytecode support. The SystemC bytecode is supported by the SystemC Emulation Engine. The SystemC emulation engine can run on any development platform that supports a basic interface of a number of different peripherals, memories, and internal components. The SystemC emulation engine's core is a SystemC emulation kernel. The SystemC emulation kernel consists of a lean event-driven kernel, a virtual machine to execute the SystemC bytecode instructions, and hooks and access to the development platform's peripheral set. We demonstrate the usefulness of the SystemC-on-a-Chip framework by developing several complete SystemC-on-a-Chip platforms, highlighting that writing SystemC applications follows the same "Write once, run anywhere" programming paradigm made popular by interpreted languages like Java and C#.

In Chapter 4, we show that for the common case where the SystemC-on-a-Chip is running on an FPGA, we can achieve substantial speedup over a baseline emulation engine by intelligently taking advantage of available FPGA resources. We introduce SystemC bytecode accelerators, special coprocessors that can execute the SystemC bytecode natively. SystemC bytecode accelerators are implemented using available FPGA resources, and can be numerous, allowing a SystemC application to effectively to run in parallel (compared to being a parallel simulation). The SystemC bytecode accelerators can improve SystemC emulation execution by approximately 2X. We further demonstrate that the SystemC emulation engine can make intelligent choices about how best to effectively utilize the SystemC bytecode accelerators. We define the Online *Emulation Acceleration* problem and demonstrate that we can achieve 20x improvement over the baseline SystemC emulation engine. With extra available FPGA resources, we also show that we can create custom interconnects among the SystemC bytecode accelerators. Such custom interconnects can effectively bypass the SystemC emulation kernel, and result in additional performance improvement.

Unfortunately not all platforms benefit from the resources required to instantiate multiple SystemC bytecode accelerators. In Chapter 5, we address this issue a software-based improvements that *just-in-time* compile the SystemC bytecode to the native processor upon which the SystemC emulation engine is running. Using minimal resources, we modify the SystemC-on-a-Chip framework to be *JIT Aware*, allowing the just-in-time compiled code to execute from resident small, fast memories. Our *JIT Aware* framework includes a JIT Aware Memory, and custom logic for maintaining

emulation signal and event queues. Such modifications result in speedups of approximately 10X compared to a baseline emulation engine, and at near comparable speeds to the same application developed for the native platform.

In Chapter 6, we demonstrate just-in-time synthesis of SystemC applications running on the SystemC-on-a-Chip framework. Just-in-time synthesis is a transparent process(to the SystemC application designer and to the SystemC emulation engine) that synthesizes, place and routes, and maps the original SystemC application to a native implementation that fully takes advantage of the platform's available resources. Just-intime synthesis of SystemC application results in orders of magnitude speedup of SystemC applications compared to executing natively on the SystemC emulation engine, and several times faster than simulating the SystemC application on a desktop PC.

In Chapter 7, we describe the utility of using the SystemC-on-a-Chip framework for digital physiological model development. We demonstrate *time-controllable* debug features, allowing a physiological model designer to debug using the concept of *time*. This is contrast to traditional debug approaches that require debugging at the instruction level. While instruction level debugging makes sense for traditional sequential programs, *time-level* debugging provides powerful mechanisms to the digital physiological model designer not possible with more traditional approaches.

In Chapter 8, we demonstrate tools and materials useful for teaching a course on spatial programming with SystemC. We develop a freely available Windows-based framework to compile, connect, and download SystemC descriptions to popular teaching development platforms. We also present possible course materials, including web materials, and course lessons.

We demonstrate the feasibility of using SystemC as a portable distribution language for FPGA applications. We demonstrate the portability of such a portable distribution by developing a fast SystemC emulation framework that transparently optimizes the SystemC application, allowing SystemC applications to *immediately* run without costly and hard-to-use synthesis/mapping tool flows.

### Chapter 2

## **Spatial Algorithms**

### 2.1 Overview

As FPGAs become more common in mainstream general-purpose computing platforms, distributing high-performance implementations of applications on FPGAs will become increasingly important. We present a study entitled *C is for Circuits* that shows that while many manually created circuits can be captured in a sequential language like C for portability purposes, often those implementations would still benefit from explicit parallel concepts. We then investigate the requirements for a language for spatial capture of FPGA applications, and conclude that SystemC satisfies such requirements.

### 2.2 C is for Circuits

### 2.2.1 Overview

It is now well-established that many sequential algorithms captured in a language like C can be synthesized to exceptionally fast circuits on field-programmable gates arrays. Numerous FPGA synthesis tools exist [39][49][57][104], with commercial offerings

beginning to appear [24][25][76], and commercial computing platforms increasingly supporting FPGAs [77][119]. Capturing algorithms in C code (or a similar sequential language, which for simplicity we'll refer to as C code henceforth) provides tremendous portability advantages, as code can be compiled to a microprocessor, or synthesized entirely or partially to FPGAs available on a computing platform. Yet, designers still often conceptualize and capture applications as circuit designs, rather than as C code. While this situation is partly explained by the relatively nascent state of FPGA compilation tools, a significant contributor is also the radically different computation model provided by C than by circuits. The sequential instruction model of C is oriented to time-ordered execution of instructions, while circuits are oriented to spatial connectivity of concurrently-executing components.

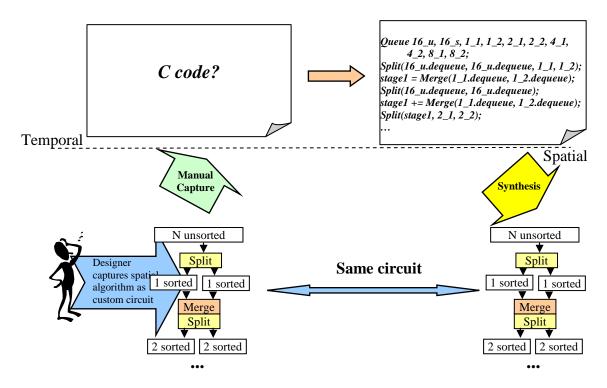

In contrast to the advent of compilers causing assembly coding to be almost entirely replaced by C coding, where both coding styles were temporally oriented, the sharp distinction between temporal and spatial models likely means that spatial models will persist in some form despite continued maturation of C-based FPGA synthesis. Spatial models, such as circuits, possess tremendous degrees of design freedom. Much human ingenuity often underlies the design of both custom circuits and what are known as "hardware algorithms," which often look radically different from sequential code algorithms designed to solve the same problem. (Because "hardware algorithms" is a misnomer in the era of FPGAs, which implement circuits as software, we use the term "circuit-based algorithms"). Figure 2 shows that while a standard synthesis tool might be able to generate a number of different circuits based on the temporally-oriented Quicksort algorithm, no amount of transformations would be likely to discover a systolic array circuit implementation for fast sorting.

Although circuits represent an important application capture method, capturing applications as circuits suffers from limited portability. A circuit, captured at the netlist level or even at the register-transfer level, cannot readily be adapted to FPGAs differing in their capacities or hard core resources, nor be compiled to execute on a microprocessor. Improved portability could increase the present usefulness of an application across platforms, while also increasing its longevity. In contrast to a circuit, an algorithm captured in C code has much portability. C code can be synthesized to FPGAs of differing capacities and hard core resources, through transformations like loop unrolling and through scheduling, allocation, binding, and technology mapping. C code can even be partitioned among a microprocessor and FPGA, or run on a microprocessor (or several microprocessors) without any FPGAs at all.

We therefore asked the following question:

To what extent can human-designed circuit implementations of an application be captured in a form of C code that can be expected to be synthesized back to the same human-designed circuit?

Note that this question has a subtle but critical difference from most past research that instead seeks to convert an *existing* sequential algorithm to a circuit [39][43][49][64][104][126][129] – research that clearly has much utility. To the best of our knowledge, the above question has not been directly addressed by the codesign or synthesis communities.

Several previous works are related to the question. Stitt [130] provides guidelines for C coders to yield improved circuits. Haubelt [63] formally analyzes a high-level description's flexibility, meaning the extent to which the description can be synthesized to a wide variety of circuits.

Other works are also related. Work on reverse engineering of circuits [40][59] has focused on obtaining low-level behavioral models, like Boolean equations or finite-state machines, for retargeting to different silicon technologies. Those works are not intended for targeting microprocessors. Early hardware/software partitioning work moved noncritical circuit functionality from circuits to microprocessor code [58]. SystemC [46], involving libraries and macros added to C++, allows for temporal and spatial concepts to be captured in a single C++ description.

Of course, circuit designers who use synthesis tools regularly use knowledge of synthesis techniques when writing behavioral (e.g., register-transfer-level) descriptions, such as writing a for loop that can easily be unrolled. Likewise, parallel architecture programmers write simpler code (e.g., loops) they know compilers will transform to parallel code. The question we seek to answer takes circuit techniques to a higher level, and differs from parallel programming techniques in the finer granularity of parallelism offered by FPGAs compared to more standard parallel architectures.

None of the above works explicitly addresses whether existing circuits can be captured in a temporal language. Answering this question is relevant to the FPGA and codesign communities, to determine the extent to which C code can be used to distribute circuit-based algorithms to different compute platforms – algorithms that today are commonly captured and distributed as circuit or register-transfer-level designs.

### 2.2.2 A Motivating Example – Sorting

There are numerous factors a designer must consider when implementing a sorting algorithm, including data set size, data ordering, and now more recently, the platform on which the algorithm will run.

A software designer targeting a microprocessor platform might use a classic temporal sorting algorithm, such as Quicksort[69], which recursively divides the data into sets greater than and less than a selected pivot. In contrast, a designer targeting an FPGA might approach the problem differently, instead relying on spatial constructs to capture the notion of sorting. The designer might use a systolic Mergesort [154] or Bitonic sort [17], representing highly-parallel, pipelined sorting methods, which cannot reasonably be expected to be derived from a Quicksort algorithm by any FPGA compiler (Figure 2).

Figure 3: C is for circuits: Some circuits might still be captured in a form of C code that is synthesizable back to the original circuit; such C code would provide tremendous portability advantages over other circuit representations

Those methods are radically different than the temporal Quicksort algorithm, even though they accomplish the same task.

Unfortunately, a systolic Mergesort circuit representation is typically not portable, often distributed as a bitstream or at best, some form of netlist. The lack of portability forces distributors to design not only different circuits for different data set sizes, but also for different FPGA sizes and families, which could easily number in the hundreds. Figure 3 illustrates the portability benefits of capturing circuits as C code, showing that if we can capture the systolic Mergesort circuit in *some* form of C code that could be synthesized to the original circuit, we would have a more robust distribution format, capable of being run on a wide range of platforms.

#### 2.2.3 Study Methodology

To investigate whether circuits designed for FPGAs might be captured and synthesized from C code, we examined all papers from six years of the IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM 2001-2006), a forum for presentation of clever human-designed circuits for FPGAs (among other topics). We found 70 papers that focused on description of new circuit-based algorithms or clever circuit implementations of standard algorithms for some application. After estimating that each example would require 2-3 days of investigation, we decided to investigate in-depth half of those circuits. We pseudo-randomly chose the subset of 35 circuits to investigate by sorting the 70 circuit papers according to their appearance in the proceedings, starting from oldest to newest. We chose every other paper for investigation – we explain this to make clear that the circuits were not handpicked based on their suitability for C code representation.

We then strove to find C code descriptions for the circuits that would compile back to the same circuit. The goal of the study was to find *any* C description that would compile to the human-designed circuit. Specifically, the claim is not that all functionally equivalent C algorithms would compile to that circuit. Only one is needed, and that one would be used to distribute the circuit-based algorithm. Furthermore, the goal is not to automate the derivation of the C code from the circuit, but merely to determine if a competent designer could capture his/her circuit in C code if necessary.

If we were able to capture the circuit in C code that would synthesize back to the same circuit, we classified the circuit as *"re-derivable from C"*.

Note that if we failed to classify the circuit as *re-derivable from C*, another C algorithm for the application likely exists that would synthesize to some other circuit with the same functionality, just not the same circuit as the human-designed one. That other circuit would likely have slower performance.

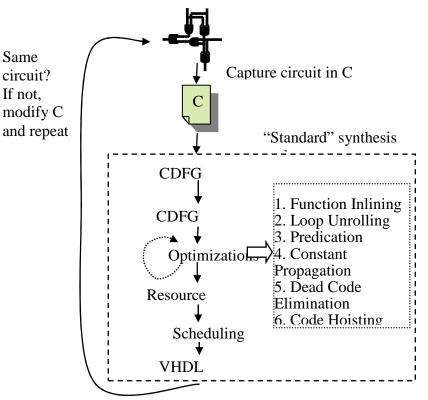

We further sub-categorized the circuits that we found to be *re-derivable from C* as either synthesizable from "*temporally-oriented C*" or "*spatially-oriented C*". We define "*temporally-oriented C*" as the obvious algorithm that most simply captured the desired behavior of the application (e.g., what we feel is the most "natural" algorithm). If we failed to find such a C algorithm, we next tried to capture the circuit's unique spatial features, through careful use of subroutines and loops, such that a reasonable FPGA synthesis tool should yield the original circuit again. While noting whether circuits were captured in *temporally-oriented* and *spatially-oriented C* was not the main point of the study, the distinction does provide some notion of the effort required by designers to capture their circuit in C code, with spatially-oriented C being harder to write. Furthermore, the distinction also shows the extent of the cleverness of the humandesigned circuit, with those derivable from the spatially-oriented C rather than temporally-oriented C likely exhibiting more complex or novel circuit design features. Because FPGA synthesis tools are still maturing and presently differ widely, we did not simply run the C algorithm through one particular tool. Instead, we defined the transformations and optimizations that could be expected in a mature "standard" synthesis tool. The reader may thus determine for him/herself whether the transformations are "standard" enough to be applied by synthesis tools. To perform synthesis, we followed the methodology shown in Figure 4. If we were able to capture the circuit in C, we converted that C code into a control/data flow graph. We optimized the graph by performing the following optimizations in the order shown: function inlining, loop unrolling, predication, constant propagation, dead code elimination, and

**Figure 4:** Study methodology. We modeled each circuit in C (when possible). We then performed the following transformations and optimizations in the order shown, representing a "standard" synthesis tool, and observed whether the original circuit was recovered.

code hoisting – straightforward optimizations that could be reasonably implemented in any compilation tool. We performed definition-use analysis to verify that regions of a circuit could be pipelined straightforwardly. We performed resource allocation by allocating a resource for every operation in the dataflow graph. We could have used a more conservative resource allocation, but most of the circuits we investigated were pipelined, and therefore would not allow sharing of resources. We scheduled the graph using resource-constrained list scheduling, inserting registers between each stage of the dataflow graph. Again, we could have used a more conservative pipelining approach to save area, but we were interested in maximizing clock frequency. Next, we converted the scheduled graph into a structural VHDL representation that we then synthesized using Xilinx ISE.

Designers typically define a custom memory interface to best serve the custom circuit, yet our defined standard synthesis tool does not involve synthesis of custom memory interfaces. Since this work concentrates on capturing the compute aspect of custom circuits in C, and not the memory interface, we assume that the synthesis tool is provided with information for each circuit from which the tool can synthesize a custom interface similar to that in the custom circuit. Future work will involve developing mechanisms for providing custom interface information as well as synthesis transformations to generate custom interfaces.

Most of the custom circuits used a standard memory interface consisting of one dual-ported memory, which allows one port for reading and one for writing. This kind of memory interface allows for block transfers and single transfers, similar to many DMAs.

20

Some circuits implemented streaming data from off-chip memories, while others did not use external memory.

For each example, we targeted the specific FPGA used for each of the custom circuits in their original papers. Although we could have compared both the original circuit and synthesized circuit on newer FPGA fabrics, we felt such comparison might be unfair if the custom circuits were designed based on the characteristics of the original FPGA fabric.

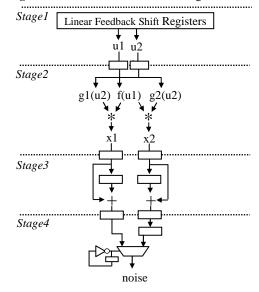

### 2.2.4 Example – Gaussian Noise Generator

Figure 5 shows the custom circuit in [88] for a Gaussian noise generator. The circuit consists of four pipeline stages. The first stage utilizes linear feedback shift registers (LFSRs) to generate a 32-bit and 18-bit random number, corresponding to *u1* and *u2*. Stage 2 uses the random numbers from the previous step as input to the illustrated functions, which consist of square root, sine, cosine, and log functions. Stage 3 adds every two consecutive results from stage 2. The circuit implements this functionality by delaying one input for a cycle using a register and then adding the output of the register with the output from the previous stage. This buffering results in a delay to the pipeline, potentially causing an output to be generated every 2 cycles. Stage 4 multiplexes the results from stage 3 to the output of the noise generator. By adding a register to the right input of the multiplexor, the circuit generates an output every cycle, instead of two outputs every two cycles.

Figure 5: Circuit for a Gaussian noise generator.

We first tried to determine if the circuit was *re-derivable from temporally*oriented C. The natural temporal C uses a loop that executes the behavior of stages 1 and 2 twice to generate two samples for the accumulate step in stage 3. FPGA synthesis tools would replicate the circuit used in each iteration of the loop, increasing the area of the circuit without improving performance. We next tried to determine if the circuit was *rederivable from spatially-oriented C*. Figure 6 shows a portion of the C code to model the Gaussian noise generator circuit in Figure 5. The C code utilizes a single function to describe each pipeline stage of the custom circuit. The output is stored into the array *noise[]*. To handle outputting to an array, we modified the code for stage 4 to store the two noise samples to two memory locations, as opposed to multiplexing the output to a single location. As we will show, this code is synthesized to the same stage 4 circuit shown in Figure 5. For simplicity, the C code uses floating point arithmetic as opposed to the fixed-point arithmetic in the custom circuit. The fixed-point code is similar, with the main difference being that the code uses logical *and* operations to remove unused bits of Figure 6: Spatial C code for Gaussian noise generator.

```

inline float rand0 1()

return rand()/((float) RAND_MAX+1);

}

inline Stage1 doStage1() {

Stage1 result;

result.u1 = rand0_1();

result.u2 = rand0_1();

return result;

}

inline Stage2 doStage2( float u1, float u2 ) {

Stage2 result;

float f_u1, g1_u2, g2_u2;

f_u1 = sqrt( -log( u1 ) );

g1_u2 = sin( 2*M_PI*u2 );

g2_u2 = cos( 2*M_PI*u2 );

result.x1 = f_u1*g1_u2;

result.x2 = f_u1*g2_u2;

return result;

}

inline Stage3 doStage3( float x1, float x2 ) {

static float acc1=0.0, acc2=0.0;

Stage3 result;

result.x1 = acc1 + x1;

result.x2 = acc2 + x2;

acc1 = x1;

acc2 = x2;

return result;

}

noise[i] = stage3.x1;

noise[j] = stage3.x2;

}

int main() {

Stage1 stage1; Stage2 stage2; Stage3 stage3;

unsigned int i=0;

while (1) {

stage1 = doStage1();

stage2 = doStage2( stage1.u1, stage1.u2 );

stage3 = doStage3( stage2.x1, stage2.x2 );

doStage4( i, i+1%NUM_SAMPLES,

stage3.x1, stage3.x2 );

i = (i+2)%NUM_SAMPLES;

}

return 0;

}

```

the random numbers, essentially specifying the width of each number to be 32 bits for u1 and 18 bits for u2.

The control and data flow graphs generated during synthesis for each function of the C code are shown in Figure 7. Figure 7(a) shows the control flow graph for *main()*,

where each function call has a corresponding node in the graph. For simplicity, we have omitted the control flow node for the code used to update the variable *i*. Figure 7(b) shows the data flow graph for function doStage1(). We omit the control flow graph for this function, and all other functions, because the corresponding graphs consist of only a single node. The data flow graph for stage 1 assigns random numbers to the two outputs of the function. Although not shown, the data flow graph also contains operations to constrain the random numbers to values between 0 and 1. Figure 7(c) and Figure 7(d) show the data flow graphs for the doStage2() and doStage3() functions. The data flow graph for doStage4(), shown in Figure 7(e), produces two outputs instead of the single output from Figure 5.

Figure 8 shows the circuits for each data flow graph for each C function after synthesis performs scheduling, resource allocation, and binding. For stage 1, shown in Figure 8(a), synthesis maps the random number generators to LFSRs. Figure 8(b) shows the circuit for stage 2, for which synthesis utilizes approximation techniques to map the

**Figure 8:** Datapaths after scheduling, resource allocation, and binding for (a) doStage1, (b) doStage2, (c) doStage3, (d) doStage3, (e) main before pipelining, and (f) main after pipelining. Note the similarity with Figure 5.

functions in stage 2 onto the same resources used to approximate these functions in the custom design. Unlike in the custom circuit, scheduling during synthesis is likely to insert registers between the approximation circuits and the multipliers in order to reduce the critical path length. For stage 3, shown in Figure 8(c), synthesis maps *acc1* and *acc2* onto registers because the outputs from this stage are used again as inputs. Stage 4, shown in Figure 8(d), multiplexes the two outputs from the data flow graph for this stage. Synthesis adds the multiplexor because the outputs from the data flow graph are written to memory, which in this case is a shared resource with only a single port. To allow both inputs to be written to memory, synthesis delays input  $x^2$  one cycle using a register while the circuit stores xI.

To optimize the circuit, synthesis can inline all of the functions for each stage into the main function and then perform code hoisting to move the code for each stage into a single control flow node, which is possible since there exists no control in each function. The resulting data flow graph for this single control node is shown in Figure 8(e). During scheduling, synthesis will insert a register at each level of the data flow graph, as shown in Figure 8(f). Note the similarity of the circuit in Figure 8(f) with the custom circuit shown in Figure 5. The only difference in the synthesized circuit is the addition of registers before the multipliers – an addition that may actually improve performance compared to the custom circuit.

The throughput of the synthesized circuit is identical to the custom circuit, with each circuit producing a noise sample each cycle. The latency of each pipeline is different, but this latency only determines when the initial output from the circuit is valid. We point out that under certain situations, the two circuits are likely to differ in other ways. For example, if the target architecture utilizes a dual-ported memory or a memory with sufficient bandwidth to simultaneously store two results, then stage 4 of the synthesized circuit will not contain the multiplexor or buffer register. This architectural difference does not affect throughput, but does affect timing, resulting in two noise samples every two cycles. To our knowledge, synthesis cannot guarantee the same timing as the custom circuit due to the lack of timing information in the C code. However, the timing difference after synthesis does not appear to be critical.

Thus, we classify this circuit as re-derivable from (spatially-oriented) C.

**Figure 9:** Molecular dynamics accelerator. (a) Code for calculating nonbonded forces. (b) Custom circuit utilizing a divided pipeline to reduce latency penalty. (c) The synthesized pipeline differs from the custom circuit by utilizing a single pipeline. The synthesized circuit must stall due to a single memory, reducing throughput.

## 2.2.5 Example – Molecular Dynamics Simulator

Scrofano [118] creates a custom FPGA accelerator for molecular dynamics simulations. The authors identify the nonbonded-forces calculations as the most time consuming region of the simulation and provide a custom circuit for those calculations.

Figure 9(a) shows the pseudocode implemented by the custom circuit. For each atom, the inner loop calculates the forces from each neighbor of the atom. The code stores the forces in the array *forceRAM*, which the following loop stores into the *forceOBM* array.

Figure 9(b) shows a high-level view of the custom circuit for the inner loop. Scrofano utilizes two separate on-board memories (OBM) to store the *positionOBM* array and the *forceOBM* array. Utilizing two memories allows the circuit to simultaneously stream position and force data without stalling, therefore achieving a maximum throughput of one force calculation per cycle. Scrofano implements the *forceRAM* array in on-chip memory to minimize the amount of read/write mode switches that would be required if the forces were stored back immediately to the *forceOBM* array. To optimize the datapath, the authors divided the pipeline into two pipelines separated by a FIFO. Dividing the pipeline reduced the latency penalty that was incurred every time the inner loop executed. The first pipeline generates output faster than the second pipeline and therefore only the latency of the second pipeline has a significant effect on performance.

If we used C code based on the pseudocode in Figure 9(a) to try and model the custom circuit, the inner loop becomes a fully pipelined circuit that streams in the force and position data. Synthesis maps the *forceRAM* array onto block RAMs, which is possible due to the small size of the array, resulting in a single pipeline that performs the same operations as the two pipelines in the custom circuit. To our knowledge, there is presently no common synthesis technique that automatically divides a pipeline as is done in the custom circuit. Such a technique may be possible, requiring analysis to best determine the placement and size of the buffer. By using a single pipeline, the synthesized circuit incurs a larger latency penalty each time the inner loop executes, as shown in Figure 9(c). The designer might instead direct the FPGA synthesis tool by altering the C code in Figure 9(a) to model the buffer that separates the two pipelines. This might be accomplished by inserting a function call to enqueue the intermediate result of the first pipeline and dequeuing a result to the input of the second pipeline. Of course, this relies on a model of a buffer the FPGA compiler can recognize. By modeling the spatial constructs of the circuit, an FPGA tool would be able to effectively recover the original circuit.

Another important difference when using the temporally-oriented code in Figure 9(a) is that the synthesized circuit uses a single memory for input. When synthesizing code to a specific architecture, the synthesis tool must use the appropriate memory architecture, which we assume to be a single off-chip memory. Therefore, the synthesized circuit must read the position and force arrays from a single memory, which does not provide sufficient bandwidth to execute the pipeline without stalls. Therefore, the synthesized circuit has a lower throughput, outputting a force calculation every two cycles. If enough on-chip RAM existed to store both arrays, or the synthesized circuit could stream data into two on-chip memories fast enough, then the synthesized circuit could perform similarly to the designer-specified circuit.

Thus, we classify the molecular dynamics circuit as *re-derivable from (spatially-oriented) C*.

# 2.2.6 Example - Cellular Learning Automata-Based Evolutionary Computing

In [62], Hariri et al. proposed a custom architecture for cellular learning automata based evolutionary computing (CLA-EC). This architecture consists of a ring of cells, each of which stores a genome. The architecture for each cell is shown in

Figure 10(a). Each cell consists of multiple learning automata (LA) that determine a new genome. The update circuit replaces the existing genome with the new genome if the fitness value of the new genome is better. The majority function uses the genome of

Figure 10: The proposed custom CLA-EC circuit consisting of a ring of (a) custom CLA-EC cells and (b) C pseudocode that synthesizes to an almost identical parallel circuit (code for cell internals is omitted).

the left and right neighbor cells to generate reinforcement signals that guide the learning automata.

An abbreviated version of the C code we used to model the CLA-EC is shown in

Figure 10(b). This code iterates over some maximum possible number of cells, which is based on the input size. For each cell, *generateNewGenome()* implements the behavior of the majority function, learning automata, and the update function. The *generateNewGenome()* function updates the new genome if the new genome is better, otherwise the function sets new genome equal to the old genome. Because *generateNewGenome()* only modifies a single cell, the loop containing the *generateNewGenome()* function has no loop-carried dependencies, allowing synthesis to parallelize the function calls by performing function inlining, loop unrolling, predication, and code hoisting.

After the *generateNewGenome()* loop completes, *updateGenomes()* updates the genome for each cell with the new genome determined by the *generateNewGenome()* function calls. By modifying the genome of each cell, the *updateGenomes()* function

creates a dependency with the *generateNewGenome()* function, which uses the genome as input. To handle this dependency, synthesis stores the genome in a register. The resulting circuit is almost identical to the custom circuit. The only difference is the addition of a multiplexor before the new genome register that either selects the output of the learning automata or the output of the genome register.

The simplicity of the C code in Figure 10(b) suggests that this implementation may also be the most natural way of writing the application in C. We classify the cellular automata circuit as readily *re-derivable from (temporally-oriented)* C.

# 2.2.7 *More Experiments*

We described several examples from the FCCM literature and our attempts to capture those designs in some form of standard C code. We now briefly highlight several other randomly selected examples before summarizing results for the entire examined set.

Tripp [138] designed a circuit to implement a large metropolitan traffic simulation (*Road Traffic*). Each cell computed car velocities and positions based on a specific rule set imposed by the designers which reflected real world traffic conditions. When we focused on the computational aspect of each cell in the network, we found the traffic design to be readily *derivable from (temporally-oriented) C*.

Bogdonav [19] designed a systolic array structure to solve matrix calculations using Gaussian elimination (*Elimination*). The authors in fact modified a temporally-oriented algorithm to achieve their circuit design. We also found the circuit to be *re-derivable from C* code. We decided to model the Gaussian elimination calculation with

| _Year of Publication | Design                  | Re-                                          | -derivable from C? Method/Reason                    |

|----------------------|-------------------------|----------------------------------------------|-----------------------------------------------------|

| 2001                 | 3D Vec. Normalization   | Yes                                          | Spatial, if online algorithms can be specified      |

| 2001                 | Efficient CAM           | No                                           | Uses dynamic FPGA routing                           |

| 2001                 | Automated Sensor        | Yes                                          | Temporal, floating point -> fixed point             |

| 2001                 | Regular Expression      | Yes                                          | Spatial, creative connections of one-bit flip flops |

| 2002                 | Hyperspectral Image     | Yes                                          | Spatial, data reordering                            |

| 2002                 | Machine Vision          | Yes                                          | Spatial, custom pipelining                          |

| 2002                 | RC4                     | Yes                                          | Temporal, straightforward implementation            |

| 2002                 | Set Covering            | Yes                                          | Spatial, data structures for easy hw implementation |

| 2002                 | Template Matching       | Yes                                          | Spatial, heavy modifications to original algorithm  |

| 2002                 | Triangle Mesh           | Yes                                          | Spatial, custom encoding scheme                     |

| 2003                 | Congruential Sieves     | Yes                                          | Temporal, straightforward translation               |

| 2003                 | Content Scanning        | Yes                                          | Temporal                                            |

| 2003                 | F.P and Square          | Yes                                          | Spatial                                             |

| 2003                 | Gaussian Noise          | Yes                                          | Spatial, requires the use of spatial C constructs   |

| 2003                 | TRNG                    | No                                           | Requires sampling a high frequency clock for noise  |

| 2004                 | 3D FDTD Method          | Yes                                          | Spatial                                             |

| 2004                 | Deep Packet Filter      | No                                           | Requires knowledge of underlying FPGA               |

| 2004                 | Online Floating Point   | No                                           | Online algorithm, variable length buffers           |

| 2004                 | Molecular Dynamics      | Yes                                          | Spatial                                             |

| 2004                 | Pattern Matching        | Yes                                          | Spatial                                             |

| 2004                 | Seismic Migration       | Yes                                          | Spatial                                             |

| 2004                 | Software Deceleration   | No                                           | Use a uP for its cache                              |

| 2004                 | V.M Window              | No                                           | Specific timing schemes implemented                 |

| 2005                 | Data Mining             | Yes                                          | Spatial                                             |

| 2005                 | Cell Automata           | Yes                                          | Temporal                                            |

| 2005                 | Particle Graphics       | Yes                                          | Spatial                                             |

| 2005                 | Radiosity               | Yes                                          | Temporal                                            |

| 2005                 | Transient Waves         | Yes                                          | Spatial                                             |

| 2005                 | Road Traffic            | Yes                                          | Temporal                                            |

| 2006                 | All Pairs Shortest Path | Yes                                          | Spatial                                             |

| 2006                 | Apriori Data Mining     | Yes                                          | Spatial                                             |

| 2006                 | Molecular Dynamics      | Yes                                          | Spatial, define separate memories, custom pipeline  |

| 2006                 | Gaussian Elimination    | Yes                                          | Spatial                                             |

| 2006                 | Radiation Dose          | Yes                                          | Temporal                                            |

| 2006                 | Random Variates         | Yes                                          | Spatial                                             |

| Totals:              |                         | 82% of the circuits were re-derivable from C |                                                     |

Figure 11: 82% of the studied circuits published in FCCM were re-derivable from C, meaning they could be captured in some form of C such that a synthesis tool could be expected to synthesize the same or similar custom design.

Totals:

82% of the circuits were re-derivable from C

*spatially-oriented C* code to ensure synthesis transformations would recover the original systolic array structure.

Krueger [86] designed a floating point unit to add two streaming numbers. The design incorporated variable delays, which we were not able to capture in either temporal or spatial C. We classified their design as *not re-derivable from C*. We again point out that there do exist C algorithms for this application that would synthesize to *some* circuit – just not to the particular published circuit.

Figure 11 summarizes all the designs studied. As described earlier, we identified 70 custom circuit designs published in the last six years of the IEEE Symposium on Field-Programmable Custom Computing Machines, of which we chose every other circuit to study in depth, totaling 35 custom circuit designs. Of the 35 designs, 29 of the designs, or 82%, were found to be *re-derivable from C*. Of the 29 circuits *re-derivable from C*, 9 of those, or 25% of all 35 circuits, were captured in *temporally-oriented C*. Again, this means these designs could have been written in natural high level code, and we could have reasonably expected a synthesis tool to recover the circuit, without much human effort at the circuit level. We note that a benefit of being able to capture the circuit as *temporally-oriented C* is that if the platform on which the circuit runs happens to be a microprocessor, the code may be able to run at or near its best performance, because the algorithm may be the same algorithm one would have written if initially targeting a microprocessor.

20 of the circuits, or 57%, were re-derivable from C were captured in *spatially-oriented C* code. There were several common reasons why a design had to be described in *spatially-oriented C* as opposed to the more natural *temporally-oriented* algorithm. Custom circuit designs often employed a combination of spatial techniques, including intricate pipelining, custom buffering, advanced memory hierarchies, and systolic array connectivity, none of which could reasonably be re-derived from the standard synthesis techniques.

For 17% of the circuits, we were unable to capture the circuit in any form of C code that would be synthesized back to that circuit. James-Roxby et. al [80] proposed

logic-centric systems in which they added microprocessors to the design to make effective use of the cache hierarchy, a technique not reasonably describable using standard C constructs. Several circuits [86][150] utilized low level cores that made rederiving from C difficult. Others [145] implemented circuits that relied on precise timing, which is also difficult to capture in C. One circuit [81] took advantage of the dynamic reconfigurability of the FPGA to implement dynamic routing, a technique clearly not supported by standard C constructs.

In summary, 82% of the circuit designs published in a forum for circuit-based algorithms could be captured in some form of standard C such that a synthesis tool supporting a basic set of transformations could recover the circuit from that C code.